|

현재 실리콘(Si) 기반 반도체는 크기가 작아질수록 전기가 새어 나가거나 성능이 급격히 떨어지는 물리적 한계에 부딪히고 있다. 이를 해결하기 위해 원자 한 층 수준으로 얇으면서도 전자를 자유자재로 조절할 수 있고 표면 결함이 없어 층층이 쌓기에 유리한 2차원 반도체가 실리콘을 대체할 핵심 대안으로 떠오르고 있다.

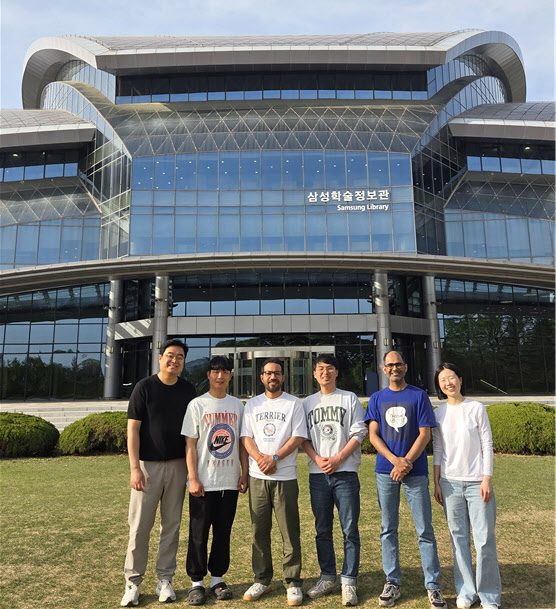

이에 공동연구팀은 n형과 p형 트랜지스터를 수평이 아닌 수직으로 쌓아 올리는 CFET 구조와 이를 하나의 칩에 통합하는 3차원 집적 기술을 적용했다. 연구팀은 8인치 웨이퍼 기준 99% 이상의 생산 수율을 달성하는 데 성공했으며 전기가 더 잘 흐르게 하는 초저 접촉저항과 높은 구동전류도 확보했다.

또 연구팀은 400도 이하 저온에서 반도체를 만드는 공정이 중요하다고 봤다. 이를 토대로 이미 만들어진 하부 소자에 열적인 손상을 주지 않고 그 위에 새로운 소자를 직접 쌓아 올릴 수 있다는 것이다. 이로써 고비용의 공정 없이도 3차원 수직 반도체를 구현할 수 있다는 것이다.

김선국 교수는 “이번 연구를 통해 2차원 반도체가 실제 양산 가능한 초고집적 소자로 자리 잡기 위해 해결해야 할 기술적 지도를 완성했다”며 “2차원 CFET 구조가 실리콘의 한계를 극복하고 미래 반도체 산업의 핵심 설계 방식으로 도약하는 데 중요한 지침서가 될 것”이라고 말했다.

.png)

.png)