|

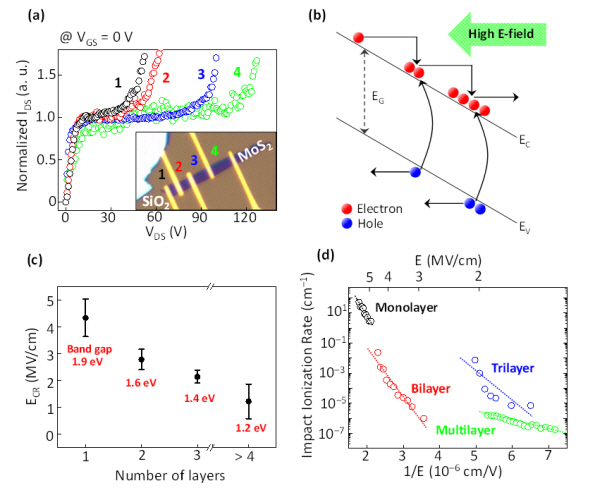

한국과학기술연구원(KIST) 광전하이브리드연구센터 정승준 박사팀과 서울대학교 물리천문학부 이탁희 교수팀은 강한 전기장 하에서 이황화 몰리브덴(MoS2) 전계효과트랜지스터(field-effect transistor, FET)의 임계전압 후의 전류 증폭이라는 독특한 물리적 현상의 원인이 ‘전자사태 항복’(애벌런시, avalanche breakdown) 현상이라는 점을 발견했다고 30일 밝혔다.

전자사태 항복 현상은 반도체 속에서 강한 전계에 의해 새로운 캐리어(전자·정공을 아우르는 말)를 발생하는 과정이 반복되고, 이때 생기는 전류의 증폭에 의해 현저하게 전기저항이 작아지는 상태를 가리킨다.

그래핀은 2차원 물질로 뛰어난 물리·화학적 특성을 가지고 있어 이를 활용해 휘어지는 기기나 웨어러블 전자기기 구현에 대한 연구가 활발하다. 그러나 FET와 같은 반도체 소자에 응용되기 어렵다는 한계가 있었다.

전자 소자의 크기가 수 마이크로미터(㎛) 이하로 작아지면서 반도체 층이 강한 전기장 환경에 노출됐을 경우에 대한 보고는 많이 있었으나, 특정 임계전압 이후 전류가 ‘증폭’하는 물리적 현상에 대한 명확한 원인 규명은 보고된 바가 없었다.

공동연구팀은 이러한 점에 주목해 연구를 진행했다. 나아가 전류 증폭의 임계전압은 이차원 반도체의 두께에 따라 변화한다는 것을 규명해, 두께가 두꺼울 때 임계전압이 낮아지고, 두께가 얇을 때 임계전압이 높아지는 점도 발견했다. 이차원 반도체의 두께에 따라 임계전압이 조절 가능하다는 점을 발견해 다양한 응용 연구에 대한 기반을 마련했다는 평가다.

정승준 박사는 “이번 연구가 점점 작아지는 이차원 반도체의 소자 크기로 인해 발생할 수 있는 물리적 현상과 전기적 특성 변화에 대한 이해도를 높이고, 향후 초박막 이차원 반도체 및 전자재료 기반 차세대 웨어러블 응용소자 구현에 핵심기반이 될 것으로 기대한다”고 밝혔다.

이번 연구결과는 과학기술정보통신부 지원으로 KIST 기관고유사업과 한국연구재단 창의연구단 과제로 수행했다. 연구결과는 ‘ACS Nano’ (IF : 13.709, JCR 분야 상위 4.23%)에 최신호에 게재됐다.

|

.png)

.png)