한국과학기술원(KAIST)은 임성갑 생명화학공학과 교수 연구팀이 유호천 가천대 전자공학부 교수 연구팀과 함께 데이터 처리 효율성과 집적도는 높인 디지털 논리 회로를 구현했다고 11일 밝혔다.

|

하지만 논리 상태가 1개 더 추가돼 세 가지 논리 신호를 모두 안정적으로 출력하기 어려웠다. 2진법 논리 체계가 3진법 논리 체계와 호환이 되지 않는 문제도 발생했다.

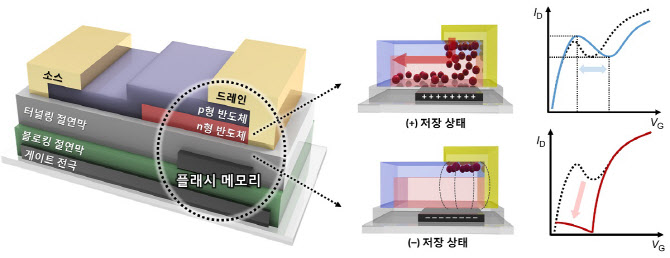

연구팀은 3진법 논리 회로의 출력 특성을 회로 동작 중에 실시간으로 조절하는 새로운 논리소자를 개발했다. 컴퓨터에서 필요에 따라 정보를 저장하거나 다시 지울 수 있는 장치인 플래시 메모리에 주목했다. 3진법 논리 회로에 정보를 저장하도록 회로를 구성하는 논리소자에 플래시 메모리를 집적했다.

그 결과, 3진법 논리 회로가 저장한 정보에 따라 논리 상태 ‘1’의 출력 특성을 조절했다. 3진법 논리 회로의 동작 안정성(잡음 여유)을 약 60%까지 달성했다.

또 3진법 논리 회로에 저장한 정보를 완전히 지우는 경우에 논리 상태 ‘1’이 출력되지 않고 ‘0’ 과 ‘2’의 두 논리 상태만 출력하는 점을 이용해 2진법과 3진법 논리 동작이 모두 가능한 회로를 만들었다.

|

유호천 가천대 교수는 “필요에 따라 2진법 연산과 3진법 연산이 자유자재로 바꿀 수 있는 반도체 소자를 개발했다”며 “기존 메모리, 비메모리 칩 규모를 줄일 수 있는 유망한 기술이 될 것”이라고 했다.

임성갑 KAIST 교수도 “기존 디지털 논리 회로와 비교해 다양한 연산이 가능하고 복잡한 연산을 단순화한 논리소자를 개발했다”며 “앞으로 대용량 정보 처리가 필요한 인공지능, 사물인터넷 등에 신개념 반도체 소자로 쓸 수 있다”고 했다.

연구결과는 국제 학술지 ‘네이처 커뮤니케이션(Nature Communications)’에 지난 23일자 온라인판에 게재됐다.

.png)

!['개과천선' 한국판 패리스 힐튼 서인영의 아파트[누구집]](https://image.edaily.co.kr/images/vision/files/NP/S/2026/05/PS26050300075t.jpg)