|

삼성전자는 현재 EUV 공정으로 14나노 초반대 ‘4세대 10나노급(1a) D램 양산 기술’을 세계 최초로 개발했다. 이 4세대 D램은 1세대보다도 12인치 웨이퍼(반도체 원판)당 생산성을 2배 높일 수 있다. 또 내년엔 성능과 용량을 더욱 높인 4세대 D램(DDR5·LPDDR5)을 양산하고, 5세대·6세대 D램도 선행 개발해 초격차 전략을 지속한다는 방침이다. 이는 현재 3세대 10나노급(1z) D램 개발 단계에 머물고 있는 미국 마이크론 등 나머지 D램 ‘빅(BIG)3’와는 1년 이상의 기술 격차다.

삼성전자는 양산 측면에선 올 하반기 평택 신규 라인을 가동해 차세대 프리미엄 D램 수요에 안정적으로 대응할 계획이다. 또 내년부터 ‘DDR5·LPDDR5’ D램 시장의 본격 확대에 맞춰 글로벌 IT 고객과 기술협력을 강화하고 업체 간 다양한 표준화 활동을 추진, 차세대 시스템에서 신제품 탑재 비중을 지속적으로 높여 나갈 계획이다.

그동안 EUV 노광기술은 메모리 반도체가 아닌 로직(시스템) 반도체에 필요한 기술로 알려져 왔다. 삼성전자가 파운드리(반도체 수탁생산)로 양산 중인 7나노급 소자에서는 약 58층의 패터닝 공정 중에 7층 정도가 EUV 공정으로 대체되고, 5나노급에선 12~14층 정도로 EUV 공정이 확장돼 수요가 급격히 늘어날 전망이다.

메모리 반도체는 다품종 소량 생산 구조인 시스템 반도체에 비해 생산량이 압도적으로 많아, EUV 관련 산업에 미치는 영향이 훨씬 크다. 삼성전자가 1x급 D램 양산에 1개 정도의 EUV 공정을 적용했다는 발표가 커다란 반향을 일으킨 이유다. 4세대 D램에서는 4개 이상의 레이어(층)에 EUV가 적용될 전망이다.

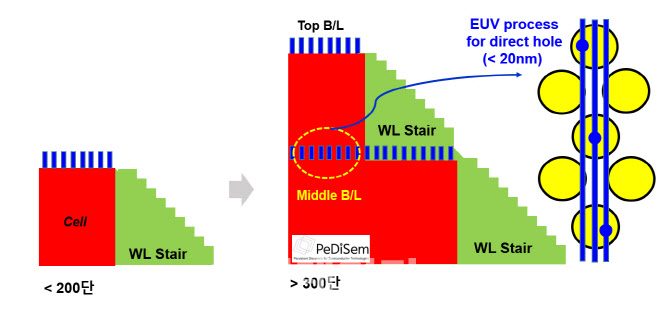

최근엔 D램 뿐 아니라 낸드플래시에서도 EUV를 적용하는 산업 전반에 고무적인 메모리 특허 기술이 나왔다. EUV 노광공정을 3D 낸드플래시 메모리(V낸드)에 적용할 수 있다면, 최첨단 로직 및 메모리 반도체 전체에 필수적인 기술이 될 것으로 보인다. 국내 스타트업이 제안한 이 기술은 V낸드에서 고(高)단으로 갈수록 길어지는 수직 채널에 기인한 셀 특성 열화 문제를 극복하기 위해 채널 중간에 센싱용 배선라인을 삽입하는 방식이다. 이를 구현하기 위해 미세한 ‘미들비트라인’ 배선과 ‘플러그홀’ 패턴에 EUV 노광기술을 사용한다면 관련 시장은 폭발적으로 확대될 수 있다.

.png)

.png)

![두손·두발 자유 테슬라 FSD 감독형 체험해보니[잇:써봐]](https://image.edaily.co.kr/images/Photo/files/NP/S/2026/04/PS26042701529t.jpg)