훗날 이 강연은 나노 기술 영감의 시초로 역사에 남게 됩니다. 오늘날 나노기술은 의류·화장품·바이오 등 실생활 속 다양한 제품과 만나며 모습을 드러내고 있습니다. 특히 반도체 분야에선 보이지 않는 나노 전쟁이 펼쳐지고 있는데요. 반도체 극초미세 공정을 가능하게 한 극자외선(EUV) 기술 세계로 들어가 보겠습니다. <편집자주>

|

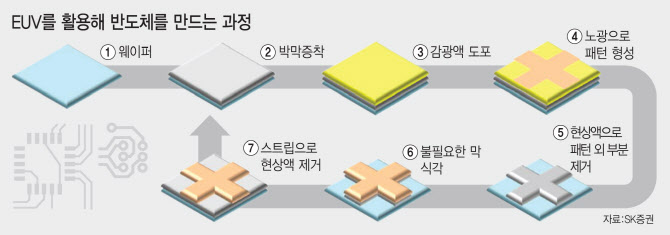

반도체의 발전은 미세화를 통해 트랜지스터 회로의 집적도(1개의 반도체 칩에 들어가는 소자의 수)를 높이면서 이뤄져 왔습니다. 반도체 업체들은 이를 위해 더 미세한 회로를 그릴 수 있는 빛을 필요로 했습니다. 반도체는 기판(웨이퍼) 위에 빛에 반응하는 감광제(포토레지스트)를 덮은 후 회로 패턴을 따라 빛을 쪼이면서 빛에 닿은 부분만 깎거나 그 부분만 남기는 방식으로 밑그림을 그려 전류가 통하게 만들기 때문입니다.

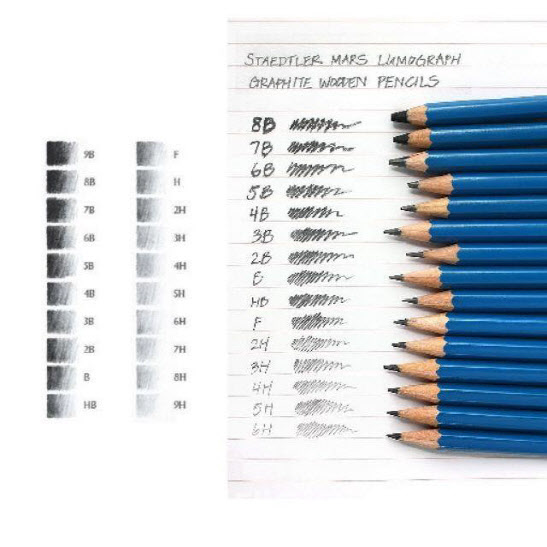

회로를 그릴 때 빛의 파장이 짧으면 짧을수록 더 가는 회로를 만들 수 있었습니다. 1980년대에는 수은 램프를 이용한 G-line(436nm 파장)과 I-line(365nm 파장) 빛을 이용했습니다. 이후 자외선 레이저인 플루오린화크립톤(KrF·248nm 파장)과 플루오린화아르곤(ArF·193nm 파장)이 개발돼 선폭을 줄이는 데 활용했습니다. 그러나 ArF에서 10nm(나노)급 반도체를 만드는데 한계에 봉착합니다. 이보다 더 정교한 회로를 그릴 수 있는 빛이 필요한 것이죠.

|

전 세계 파운드리(반도체 수탁업체) 1위인 대만의 TSMC와 삼성전자는 인공지능(AI), 5세대(5G)이동통신, 사물인터넷(IoT) 등을 기반으로 한 제품에 필요한 고성능·저전력·초소형 시스템 반도체를 만드는데 EUV를 활용하고 있습니다. 또 미세 공정 경쟁이 치열한 시스템반도체 분야뿐만 아니라 메모리반도체 D램에서도 고성능·초소형 반도체의 요구가 올라가면서 집적도를 높일 수 있는 EUV기술을 도입하는 업체들이 늘어나고 있습니다. 현재 D램에서 EUV기술을 도입한 곳은 삼성전자를 필두로 SK하이닉스, 마이크론 등이 있습니다.

|

EUV공정을 도입하면 생산 비용과 시간을 절감할 수 있다는 것이 핵심입니다. 기존에 비슷한 위치에 회로 모양을 2회 이상 찍어 내는 멀티 패터닝을 한 번에 끝낼 수 있어 칩 사이즈가 작아지고 공정 스텝 수를 줄여 원가를 절감할 수 있는 것이죠. 특히 반도체의 수십 개의 층 중에서 회로구성이 복잡해 난이도가 높은 패턴을 EUV를 활용하면 수율을 높여 생산성이 증대됩니다. 예를 들어 삼성전자는 초기 4세대 10나노급 D램(1a)에서 가장 복잡한 회로 구성인 비트라인 레이어에만 EUV를 활용해왔습니다. 이제 1a D램에선 레이어 5개에 EUV를 활용하고 있습니다.

SK하이닉스의 경우 1a에서 EUV를 쓴 버전과 안 쓴 버전을 동시에 개발하고 있는데요. D램 캐파(생산능력)의 절반 정도를 차지하는 중국 우시공장이 미국의 규제로 인해 EUV 장비가 사용되지 못할 것을 감안한 것입니다.

|

하지만 EUV를 적용하는데에도 문제가 있습니다. EUV는 현재 네덜란드 장비 회사 ASML이 독점 생산하고 있는데 장비 단가가 한 대에 2500억에 달합니다. 도입 초기라서 효율과 원가에서 충분한 효과를 보지 못하고 있습니다. 아직 EUV 1대의 하루 웨이퍼 생산량은 기존 DUV장비(4500대)의 3분의 1인 1500대 수준입니다. 비싼 가격에 초기 수율이 낮은 점을 고려하면 향후 1여년은 기존의 장비 대비 뛰어난 효율을 보기 어려울 것이라는 게 업계 추정입니다.

또 EUV는 모든 물체에 흡수되는 굉장히 까다로운 성질을 가지고 있어 핵심 설비와 관련 부품, 소재, 장비 등을 모두 새롭게 적용해야 합니다. 심지어 공기에만 노출돼도 EUV 광원을 흡수해버려 기존 공정과는 전혀 다른 프로세스를 활용해야 하는데요. 예를 들어 기존 노광장비는 투영렌즈를 활용해 ‘축소 투영’방식으로 웨이퍼에 회로를 그렸다면 EUV광원은 투영렌즈로는 높은 흡수성때문에 빛을 통과시키지 못하고 흡수해버립니다. 따라서 장비 내 반사경을 여러 개 만들어 빛의 반사 원리로 수십 번 축소 투영해야 합니다.

소재도 마찬가지입니다. EUV공정에서는 90%이상의 투과율과 50나노급의 얇은 펠리클이 필요합니다. 펠리클은 얇은 박막인데 반사 구조인 EUV 장비에선 광원 손실이 크기 때문에 투과율이 높은 펠리클이 필요합니다. 또 EUV용 마스크는 개당 가격이 수억원씩 해 먼지로 인한 마스크 손상을 최소화하기 위해 필수적입니다. 하지만 EUV용 펠리클은 최근에서야 개발이 이뤄지면서 삼성전자는 2023년에서야 펠리클을 본격 도입할 계획입니다. 그만큼 아직까지 EUV 공정을 극대화해 활용할 만큼 소재·부품·장비 등 관련 생태계가 완벽히 조성되지 않은 상황입니다.

빛의 발전은 EUV에서 멈추지 않습니다. ASML은 차세대 EUV라고 불리는 ‘High-NA EUV’장비를 2025년 양산될 전망입니다. 하이 NA EUV는 EUV 장비 해상력을 높여 보다 미세한 반도체 회로를 구현할 수 있는 장비로, 최근 인텔이 첨단 공정을 위해 ASML 하이 NA EUV 장비를 우선 공급받기로 하면서 업계 주목을 받고 있습니다. 이 장비는 7~8nm 파장의 빛을 만들 것으로 예상됩니다. 향후 EUV를 활용한 반도체 시장은 더욱 커질 것으로 예상됩니다. ASML은 오는 2025년이면 EUV 노광 장비가 전체 리소그래피 시장에서 차지하는 매출액 비중이 85%에 달할 것이라고 전망했습니다.

|

.png)

.png)